## Si LSI Process Technology for Integrating Ferroelectric Capacitors

Koji Arita, Eiji Fujii, Yasuhiro Shimada, Yasuhiro Uemoto, Toru Nasu, Atsuo Inoue, Akihiro Matsuda, Tatsuo Otsuki and Nobuyuki Suzuoka $^1$

Electronics Research Laboratory, Matsushita Electronics Corporation, 1-1 Saiwai-cho, Takatsuki, Osaka 569

Microcomputer Division, Matsushita Electronics Corporation, 1 Kotari-yakimachi, Nagaokakyo, Kyoto 617

(Received May 9, 1994; accepted for publication June 18, 1994)

The fabrication procedure of ferroelectric thin film capacitors onto conventional Si LSIs is investigated. Electrical characteristics of the integrated  $Ba_{1-x}Sr_{x}TiO_{3}$  (BST) capacitors and the metal-oxide-semiconductor transistors embedded in the Si substrate are examined. Results of these measurements suggest the usefulness of this integration process for the fabrication of ferroelectric thin film devices, which is substantiated by the evaluation of an analog/digital IC with the integrated BST bypass capacitor.

KEYWORDS: ferroelectric, fabrication procedure, metalorganic deposition, Ba<sub>1-x</sub>Sr<sub>x</sub>TiO<sub>3</sub>, leakage current, time-dependent dielectric breakdown

#### 1. Introduction

Within the last several years, ferroelectric thin films have attracted much attention because of their electronic and electrooptic applications, which has brought about new and significant developments in this field. From the viewpoint of the semiconductor industry, some of the application areas for ferroelectric thin films are of the most recent interest, such as high-density dynamic random-access memories (DRAMs). 1) nonvolatile memories, 2) metal-ferroelectric-semiconductor devices, 3) and LSIs with integrated bypass capacitors. 4) The fabrication procedure of ferroelectric thin film capacitors into conventional Si LSIs, however, is not yet well established, though some laboratories are prototype low-density nonvolatile manufacturing memories.<sup>5)</sup>

This paper describes our process technology for integrating ferroelectric thin film capacitors into Si LSIs, which can be applied to various kinds of ferroelectric thin film devices. It should be mentioned that throughout this paper the term "ferroelectric" is used to describe these films even though the hysteresis characteristics provided by spontaneous polarization are not utilized in the devices described later.

#### 2. Integration of Ferroelectric Capacitors on Si LSIs

## 2.1 Preparation of ferroelectric thin films

In this study we chose  $Ba_{1-x}Sr_xTiO_3$  (BST) as a high-dielectric material, and the BST thin films were deposited by a spin-on technique called metalorganic deposition (MOD).<sup>1,6)</sup> It should be noted here that the capacitor fabrication process below is not affected by the deposition methods of the ferroelectric thin films, such as sputtering,<sup>7)</sup> laser ablation,<sup>8)</sup> metalorganic chemical vapor deposition (MOCVD),<sup>9)</sup> and liquid source CVD.<sup>10)</sup> For the preparation of the MOD-derived thin films, a mixture of metal alkoxides corresponding to the required ferroelectric thin films was used in the spin-coating process, followed by the drying and sintering processes.

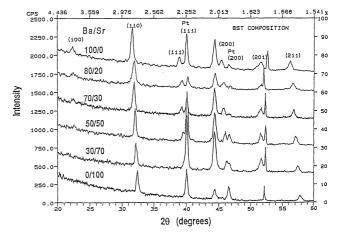

Figure 1 shows the X-ray diffraction patterns for the BST thin films deposited at different Ba/Sr ratios.

These spectra indicate that these films have a polycrystalline phase with no orientation. In comparison with the lattice constant of each BST film, which was calculated from these X-ray peaks, and that of BST ceramics, it is found that the lattice constant of the BST film changes in the same manner as bulk ceramics, <sup>1,6)</sup> which suggests crystallographic and electrical similarities between the thin films and bulk ceramics. Since the BST system has the crystal phase transition between tetragonal and cubic at the Sr composition of 0.3, <sup>11)</sup> the largest dielectric constant among all of these compositions can be expected at this optimum composition.

### $2.2 \quad Fabrication \ procedure$

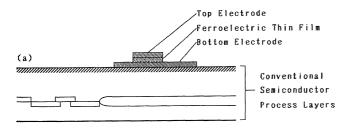

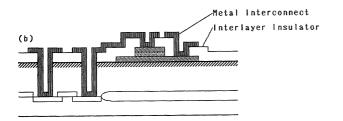

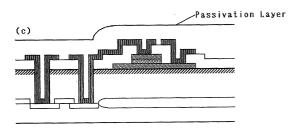

A schematic illustration of the fabrication process of the ferroelectric thin film capacitors is shown in Fig. 2. The ferroelectric process layers are formed after the fabrication of the conventional metal-oxide-semiconductor (MOS) transistors onto the Si substrate, where the  $SiO_2$  layer is deposited on the surface.

First, the bottom Pt electrode is vapor-deposited on the substrate. To obtain good adhesion, a Ti layer is formed between the Pt electrode and the substrate. <sup>12)</sup> Then, the ferroelectric thin film is deposited on the Pt electrode by the above-mentioned MOD technique.

Fig. 1. X-ray diffraction patterns of the  ${\rm Ba_{1-x}Sr_xTiO_3}$  thin films. Sintering temperature: 750°C. Film thickness: 160 nm.

Fig. 2. A schematic illustration of the fabrication process of integrated ferroelectric capacitors.

After that, the top Pt electrode is vapor-deposited on the ferroelectric thin film, and its patterning is carried out with use of the ion milling method or the reactive ion etching (RIE) technique<sup>13)</sup> to create the ferroelectric thin film capacitors (Fig. 2(a)).

As an interlayer insulator, a SiO<sub>2</sub> thin film is deposited over the ferroelectric capacitors by CVD. A Ti film is vapor-deposited on the top Pt electrode before the etching of the ferroelectric process layers in order to obtain good adhesion to the CVD-deposited SiO<sub>2</sub> layer.

The subsequent fabrication process, which consists of the metallization process for the interconnection (Fig. 2(b)) and the passivation process followed by the formation of bonding pads (Fig. 2(c)), is equivalent to the standard Si LSI process. It should be noted that in the metallization process a barrier layer is required between Al and Pt because Pt tends to react with Al to form  $Al_2Pt$ , whose growth sometimes causes the metallization degradation. Currently we employ TiW as a barrier metal. As a passivation layer,  $Si_3N_4$  is deposited by plasma CVD at present.

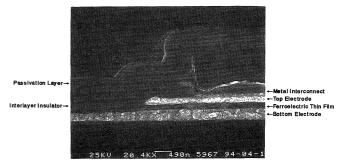

Figure 3 shows the scanning electron micrograph of the integrated  $Ba_{0.7}Sr_{0.3}TiO_3$  (BST(70/30)) thin film capacitor. For the patterning of this BST capacitor, the RIE technique was utilized.

# $\begin{array}{cccc} 2.3 & Characteristics & of & integrated & ferroelectric \\ & capacitor & \end{array}$

For electrical characterization of the integrated ferroelectric thin film capacitors, BST(70/30) capacitors

Fig. 3. Scanning electron micrograph of the integrated  $Ba_{0.7}Sr_{0.3}TiO_3$  capacitor. Due to the limit of sensitivity of our instrument, the boundary between the interlayer insulator  $(SiO_2)$  and the passivation layer  $(Si_3N_4)$  is not clear.

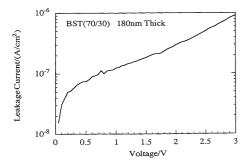

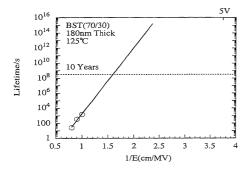

were formed onto the Si substrate where MOS transistors had already been fabricated, using the above-mentioned procedure. Figure 4 shows the leakage current characteristics of the integrated MOD-deposited 180 nm BST(70/30) capacitor measured at room tempera-The leakage current density was around  $1.2 \times 10^{-7}$  A/cm<sup>2</sup> at 1 V. This suggests that the integrated BST capacitor is applicable to highly integrated memories such as 256M DRAM. Its time-dependent dielectric breakdown (TDDB) characteristic is shown in Fig. 5, which was taken at 125°C. From the extrapolation of the experimental results in the same manner as the case of SiO<sub>2</sub>, the lifetime to breakdown of the cell capacitor is concluded to be over 10 years even under a stress voltage of 5 V. These results indicate the suitability of the integrated BST capacitors for electrical use, which is also supported by the results of the measurements of other electrical properties of the integrated BST capacitors.

Electrical characteristics of the embedded MOS transistors were also examined, which reveal that these transistors are not damaged by this integration process. This indicates the compatibility of this process with conventional semiconductor processes.

#### 3. Application to Integrated Bypass Capacitor

To demonstrate the validity of the integrated ferroelectric thin film capacitors, we have experimentally fabricated an analog/digital Si IC which integrates about 3800 transistors, and the BST(70/30) capacitor which functions as a bypass capacitor. By building the bypass capacitor which must have a large capacitance (on the order of hundreds pF) in a chip, the supply voltage is effectively stabilized and the electronic noise is reduced. Reduction of external pins and external bypass capacitors and decrease of the package size are also expected.

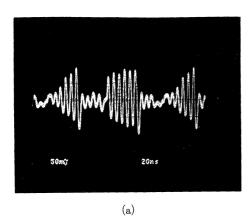

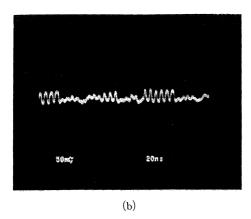

The capacitance of this integrated BST capacitor was 1400 pF. The analog/digital Si IC with a conventional 40 pF SiO<sub>2</sub> bypass capacitor instead of the BST bypass capacitor was also fabricated as a reference. Comparing the waveforms of the supply voltages shown in Figs. 6(a) and 6(b), fluctuation of the supply voltage is seen to be effectively suppressed with use of the integrated BST bypass capacitor. According to the frequency analysis, integrating the BST(70/30) bypass

Fig. 4. The leakage current characteristics of the integrated  ${\rm Ba_{0.7}Sr_{0.3}TiO_3}$  capacitor measured at room temperature. Film thickness: 180 nm.

Fig. 5. TDDB characteristics of the integrated  $Ba_{0.7}Sr_{0.3}TiO_3$  capacitor measured at 125 °C. Film thickness: 180 nm.

Fig. 6. (a) The waveform of the supply voltage of the Si IC with the  $40~\rm pF~SiO_2$  bypass capacitor. (b) The waveform of the supply voltage of the Si IC with the  $1400~\rm pF$  integrated  $Ba_{0.7}Sr_{0.3}TiO_3$  capacitor.

capacitor leads to a 70% decrease in the amplitude of electronic noise, in comparison with the conventional IC with the  $SiO_2$  bypass capacitor. This indicates that the BST bypass capacitor effectively reduces the electronic noise from signal processors, which is now a serious concern for digital equipment.

#### 4. Conclusions

The fabrication procedure of ferroelectric thin film capacitors onto conventional Si LSIs has been presented. Through device characterization of the integrated ferroelectric capacitors themselves and the Si LSIs with the integrated ferroelectric bypass capacitors, the validity of integrating ferroelectric thin film capacitors on Si devices has been clarified.

The use of ferroelectric thin films, which can be realized by this fabrication process, will be a promising method of producing various new kinds of semiconductor devices.

#### Acknowledgments

The authors would like to thank Dr. G. Kano for his advice and encouragement during this work, and Professor C. A. Paz de Araujo (University of Colorado at Colorado Springs) for collaboration in the development of ferroelectric thin film devices.

- E. Fujii, Y. Uemoto, S. Hayashi, T. Nasu, Y. Shimada, A. Matsuda, M. Kibe, M. Azuma, T. Otsuki, G. Kano, M. Scott, L. D. McMillan and C. A. Paz de Araujo: *IEDM Tech. Dig.*, Washington, D.C., 1992, p. 267.

- 2) J. F. Scott and C. A. Paz de Araujo: Science 246 (1989) 1400.

- S. Sinharoy, H. Buhay, D. R. Lampe and M. H. Francombe: Proc. 4th Int. Symp. Integrated Ferroelectrics, Monterey, 1992, p. 290 and references therein.

- S. Nagata, T. Ueda, A. Noma, H. Koizumi, K. Kanazawa, H. Ishida, T. Ueda, T. Tanaka, D. Ueda, M. Kazumura, G. Kano and C. A. Paz de Araujo: ISSCC Dig. Tech. Pap., San Francisco, 1993, p. 172.

- 5) T. Sumi, N. Moriwaki, G. Nakane, T. Nakakuma, Y. Judai, Y. Uemoto, Y. Nagano, S. Hayashi, M. Azuma, T. Otsuki, G. Kano, L. McMillan and C. A. Paz de Araujo: ISSCC Dig. Tech. Pap., San Francisco, 1994, p. 268.

- 6) K. Arita, E. Fujii, Y. Shimada, Y. Uemoto, M. Azuma, S. Hayashi, T. Nasu, A. Inoue, A. Matsuda, Y. Nagano, S. Katsu, T. Otsuki, G. Kano, L. D. McMillan and C. A. Paz de Araujo: IEICE Trans. Electron. E77-C (1994) 392.

- I. Kanno, S. Hayashi, T. Kamada, M. Kitagawa and T. Hirao: Jpn. J. Appl. Phys. 32 (1993) 4057 and references therein.

- M. Okuyama, J. Asano, T. Imai, D.-H. Lee and Y. Hamakawa: Jpn. J. Appl. Phys. 32 (1993) 4107 and references therein.

- H. Yamaguchi, P.-Y. Lesaicherre, T. Sakuma, Y. Miyasaka,

A. Ishitani and M. Yoshida: Jpn. J. Appl. Phys. 32 (1993) 4069

and references therein.

- L. D. McMillan, T. L. Roberts, M. C. Scott and C. A. Paz de Araujo: Proc. 4th Int. Symp. Integrated Ferroelectrics, Monterey, 1992, p. 666.

- K.-H. Hellwege and A. M. Hellwege eds.: Landolt-Bornstein Numerical Data and Functional Relationships in Science and Technology (Springer-Verlag, New York, 1981) Vol. III/16a.

- 12) H. N. Al-Shareef, K. D. Gifford, P. D. Hern, S. H. Rou, O. Auciello and A. I. Kingon: Proc. 4th Int. Symp. Integrated Ferroelectrics, Monterey, 1992, p. 181.

- 13) Work in progress.

- 14) N. Suzuoka, H. Oishi and M. Kayahara: Denki Gakkai Kenkyukai Shiryo, 1989, ECT-89-17 [in Japanese].